# **Problem Class 5**

#### Timing Constraints (Problem Sheet 4)

Peter Cheung Department of Electrical & Electronic Engineering Imperial College London

URL: www.ee.imperial.ac.uk/pcheung/teaching/ee2\_digital/ E-mail: p.cheung@imperial.ac.uk

PYKC 27 Nov 2018

E2.1 Digital Electronics

Problem Class 5 - Slide 1

### **Problem 1: Test yourself (not in tutorial sheet)**

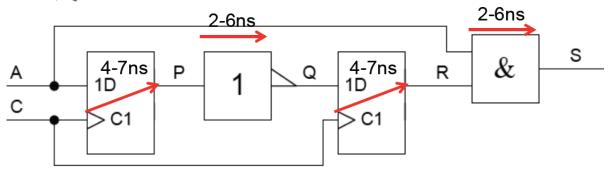

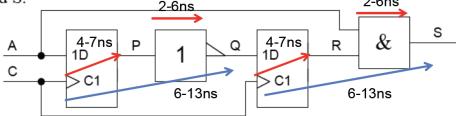

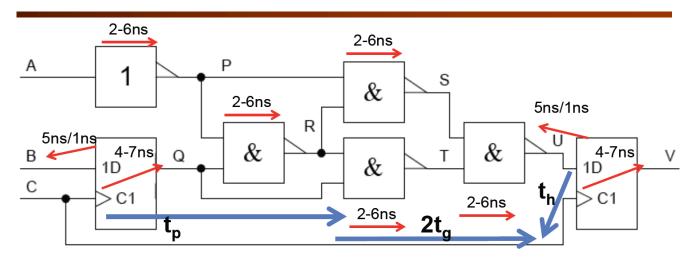

In the circuit below the propagation delay of the flipflops may vary between 4 and 7 ns while the propagation delay of the gates may vary between 2 and 6 ns.

Calculate the minimum and the maximum propagation delays from each of A and C to each of P, Q and R and S.

### Solution 1: Test yourself

Calculate the minimum and the maximum propagation delays from each of A and C to each of P, Q and R and S. 2-6ns 2-6ns

This is a trick question: there is <u>no propagation delay</u> between A and any of P, Q or R since a transition in A does not directly cause any of these other signals to change. The min and max delays from A to S are 2 and 6 ns. Of course if R happens to be low, there is no propagation delay between A and S either.

The min and max delays from C to P, Q, R and S are 4 and 7, 6 and 13, 4 and 7, and 6 and 13 ns respectively. The important point to realise is that since a transition at Q does not directly cause R to change, it follows that there is no delay path through both flipflops. The expression for a propagation delay **<u>never</u>** involves more than one flipflop delay.

PYKC 27 Nov 2018

E2.1 Digital Electronics

Problem Class 5 - Slide 3

### **Problem 2: Explain it (Not in tutorial sheet)**

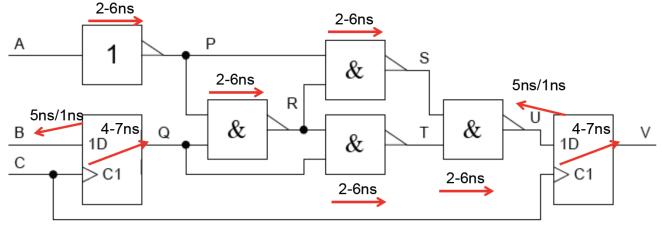

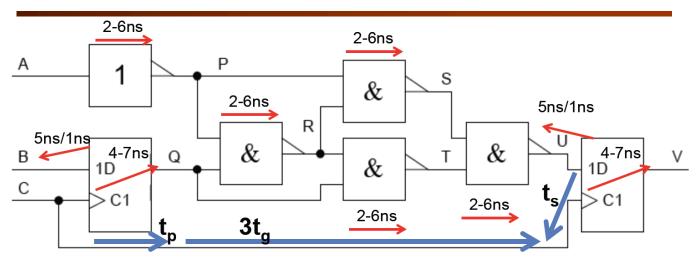

In the circuit below the setup and hold times of the flipflops are 5 ns and 1 ns respectively. The propagation delay of the flipflops may vary between 4 and 7 ns while the propagation delay of the gates may vary between 2 and 6 ns.

Calculate the minimum and the maximum propagation delays between C and U. Hence calculate the maximum frequency of the clock, C.

### Solution 2: Explain it – Setup requirement

The longest path from C to U passes through the flipflop and then through three gates: this gives a maximum propagation delay of 25 ns. This happens when  $A=0 \Rightarrow P=1 \Rightarrow R=!Q \Rightarrow T=1 \Rightarrow U=!S=R=!Q$ . We therefore use  $3t_g$  in the setup inequality below.

```

Setup: t_p + 3t_g + t_s < T \Rightarrow T > 7 + 3 \times 6 + 5 = 30 \text{ ns} \Rightarrow f < 33 \text{ MHz}

PYKC 27 Nov 2018 E2.1 Digital Electronics Problem Class 5 - Slide 5

```

#### Solution 2: Explain it – hold requirement

The shortest path from C to U passes through the flipflop and then through two gates: this gives a minimum propagation delay of 8 ns. This happens when  $A=1\Rightarrow P=0\Rightarrow R=S=1\Rightarrow U=!T=Q$ . We therefore use  $2t_g$  in the hold inequality below.

Hold:  $t_h < t_p + 2t_g \implies 1 < 4 + 2 \times 2 = 8 \checkmark$

## **Problem 3: Test yourself (Sheet 4 Q1)**

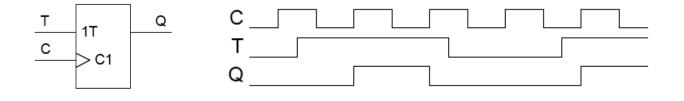

A toggle flipflop (T-flipflop) changes state whenever its T input is high on the CLOCK <sup>↑</sup> edge as shown in the timing diagram.

Show how a T-flipflop can be made by combining an XOR gate with a D-flipflop.

PYKC 27 Nov 2018

E2.1 Digital Electronics

Problem Class 5 - Slide 7

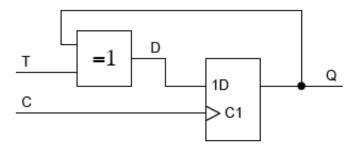

### Solution 3: Test yourself (Sheet 4 Q1)

Show how a T-flipflop can be made by combining an XOR gate with a D-flipflop.

An XOR gate can be used to invert a signal or pass it through unchanged according to whether a control input is high or low.

## **Problem 4: Explain it (Sheet 4 Q2)**

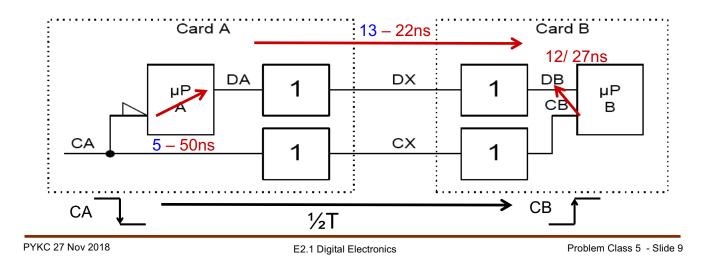

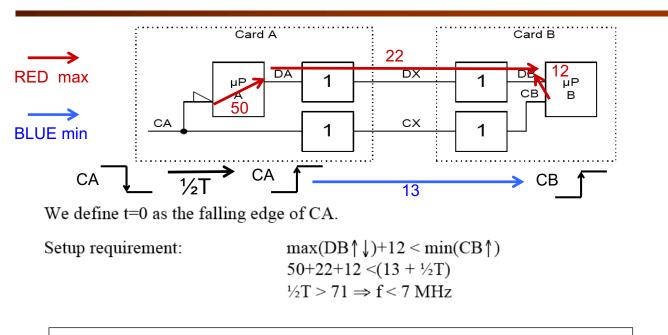

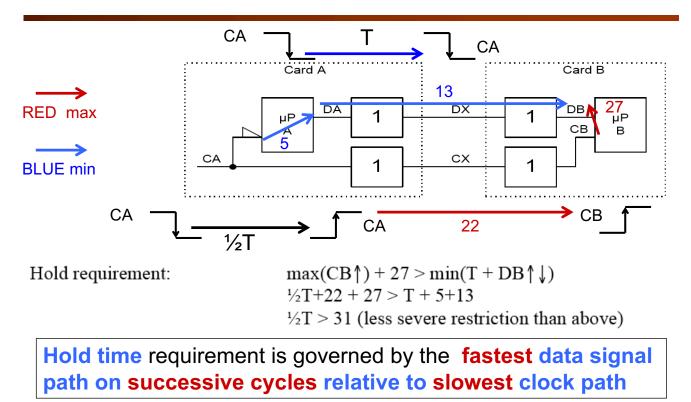

A multi-processor system contains two microprocessors which are mounted on separate printed circuit cards. The clock and data signals pass through a line driver when they leave one card and a line receiver when they pass onto the next. The combined delay of the driver+receiver may vary between 13 ns and 22 ns. New data values appear at DA on the falling edge of CA with a propagation delay of 5 to 50 ns. Data is clocked into  $\mu$ P B on the rising edge of CB with a setup time of 12 ns and a hold time of 27 ns. If the clock, CA, is a symmetrical squarewave, calculate its maximum frequency.

# Solution 4: Explain it (Sheet 4 Q2)

Setup time requirement is governed by the slowest data signal path relative to fastest clock path

## Solution 4: Explain it (Sheet 4 Q2)

PYKC 27 Nov 2018

E2.1 Digital Electronics

Problem Class 5 - Slide 11